# ACORN ASSEMBLER RELEASE 2

# ACORN ASSEMBLER RELEASE 2

Copyright © Acorn Computers Limited 1991

Published by Acorn Computers Technical Publications Department

Neither the whole nor any part of the information contained in, nor the product described in, this manual may be adapted or reproduced in any material form except with the prior written approval of Acorn Computers Limited.

The product described in this manual and products for use with it are subject to continuous development and improvement. All information of a technical nature and particulars of the product and its use (including the information and particulars in this manual) are given by Acorn Computers Limited in good faith. However, Acorn Computers Limited cannot accept any liability for any loss or damage arising from the use of any information or particulars in this manual.

If you have any comments on this manual, please complete the form at the back of the manual, and send it to the address given there.

Acorn supplies its products through an international dealer network. These outlets are trained in the use and support of Acorn products and are available to help resolve any queries you may have.

Within this publication, the term 'BBC' is used as an abbreviation for 'British Broadcasting Corporation'.

ACORN, ARCHIMEDES and ECONET are trademarks of Acorn Computers Limited.

UNIX is a trademark of AT&T.

Published by Acorn Computers Limited Release 2 ISBN 1 85250 096 4 Part number 0470,589 Product number SKD36 Issue 1, May 1991

ii

# Contents

## Contents iii

### Introduction 1

Assembler tools 1 This user guide 2 Conventions used in this manual 3

# Part 1 - Using the assemblers 5

### Assemblers and the DDE 7

Using the assemblers through Make 7 Editor throwback 8 DDT debugging 11 Using FrontEnd on your programs 15 Making your own linkable libraries 16

### AAsm 19

Starting AAsm 20 AAsm SetUp options 21 AAsm output 25 AAsm icon bar menu 26 Example AAsm session 27 AAsm managed by Make 28 AAsm command lines 28

### **ObjAsm 31**

Starting ObjAsm 31 ObjAsm SetUp options 33 ObjAsm output 37 ObjAsm icon bar menu 38 Example ObjAsm session 39 ObjAsm command lines 40

# Part 2 - Assembly language details 43

## The ARM cpu 45

Registers 46 FIQ fast interrupt request 48 IRQ interrupt request 49 Address exception trap 49 Abort 50 Software interrupt 51 Undefined instruction trap 51 Reset 52 Vector summary 52 Modes of operation 52

### Assembler language 55

Assembler language syntax 55 Symbols and labels 56 Expressions 57 Numeric constants 59 String constants 59 Boolean constants 59 Assembler operators 60 ?Label 63 Operator summary 64

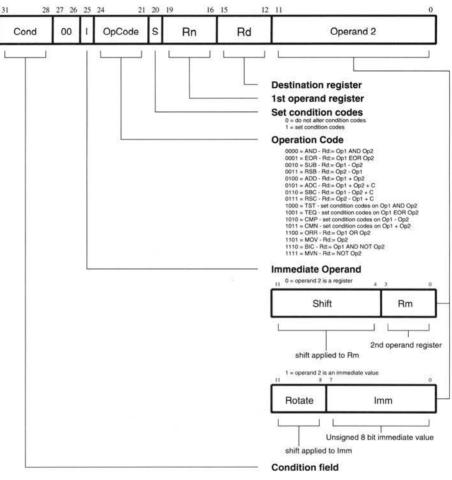

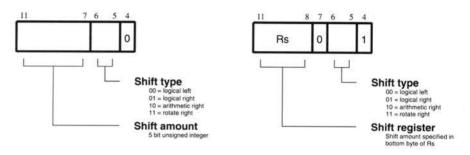

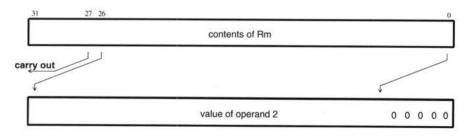

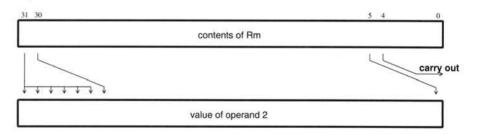

### **CPU** instruction set 65

Conditional execution 65 Instruction timing 66 The barrel shifter 68 Shift types 70 Branch instructions 72 Data processing 73 Data processing instruction syntax 74 Data processing instruction summary 79 Single data transfer 79 Single data transfer instruction syntax 80 Block data transfer 81 Block data transfer instruction syntax 82 Stacking 84 Block data transfer: special points 88 Single data swap 89 Single data swap instruction syntax 90 Multiply and multiply-accumulate 90 Multiply instruction syntax 91 Supervisor calls 92 Supervisor calls instruction syntax 92 Coprocessor instructions 93 Coprocessor data operations 93 Coprocessor data operation instruction syntax 94 Coprocessor/memory transfers 94 Coprocessor/memory transfer instruction syntax 95 Coprocessor/register transfers 95 Coprocessor/register transfers instruction syntax 96 Summary of assembler mnemonic combinations 96 Further instructions 98

### Floating point instructions 101

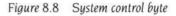

Programmer's model 101 Floating point status register 107 Floating Point Control Register 112 Assembler directives and syntax 114 The instruction set 115 Finding out more... 121

### **Directives 123**

Number equating directives: \*/EQU 123 Register equating: RN 123 Coprocessor equating: CP 124 Coprocessor register equating: CN 124 Store-loading 124 ALIGN 125 LTORG 126 Laying out storage areas 126 Variables 128 Routines and local labels 130 Error handling 132 **ORG** 133 LEADR 133 END 133 **GET 134** LNK 135 **Objasm directives** 135

#### Conditional and repetitive assembly 139

Conditional assembly 139 Repetitive assembly 141

### Macros 143

Syntax 144 Local variables 145 MEXIT directive 146 Default values 146 Macro substitution method 147 Nesting macros 148 A division macro 148

## Part 3 - Developing software for RISC OS 151

#### Writing relocatable modules in assembler 153

Assembler directives 154 Examples 155

### Interworking assembler with C 157

Examples 157

### Using memory efficiently 161

Guidelines 161 Recovery from lack of memory 161 Avoiding permanent loss of memory 162 Avoiding memory wastage 163 Using heap\_alloc and heap\_free 171

## Part 4 - Appendices 173

### Appendix A - Error messages 175

### Appendix B - Directives syntax table 183

### Appendix C - Example assembler fragments 185

Using the conditional instructions 185 Pseudo-random binary sequence generator 186 Multiplication by a constant 187 Loading a word from an unknown alignment 188 Sign/zero extension of a half word 188 Return setting condition codes 188 Full multiply 189

# Appendix D - ARM datasheet 191

**Description of signals 195**

Programmers' Model 199

Introduction 199 Registers 199 Exceptions 201

### **Instruction Set 208**

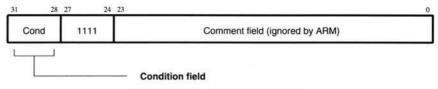

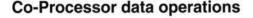

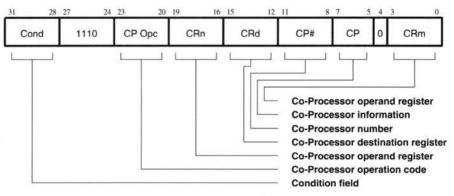

The condition field 208 Branch and branch with link (B, BL) 209 Data processing 211 Multiply and multiply-accumulate (ML) 218 Single data transfer (LDR, STR) 221 Block data transfer (LDM, STM) 226 Software interrupt 233 Co-Processor data operations 235 Co-Processor data transfers 237 Co-Processor register transfers 240 Undefined instructions 242 Instruction set summary 243 Instruction Speeds 243

Index 245

viii

# Introduction

A corn Desktop Assembler is a development environment for producing RISC OS desktop applications and relocatable modules written in ARM assembly language. It consists of a number of programming tools which are RISC OS desktop applications. These tools interact in ways designed to help your productivity, forming an extendable environment integrated by the RISC OS desktop. Acorn Desktop Assembler may be used with its sister product, Acorn Desktop C, to provide an environment for mixed C and assembler development.

Acorn Desktop Assembler includes tools to:

- edit program source and other text files

- search and examine text files

- examine some binary files

- assemble small assembly language programs

- assemble and construct more complex programs under the control of makefiles, these being set up from a simple desktop interface

- squeeze finished program images to occupy less disk space

- construct linkable libraries

- debug RISC OS desktop applications interactively

- construct template files for RISC OS desktop applications.

Most of the tools in Acorn Desktop Assembler are also of general use for constructing applications in other programming languages, and are, for example, supplied with Acorn Desktop C. These non-language-specific tools are described in the accompanying Acorn Desktop Development Environment user guide.

### Installation

Installation of Acorn Desktop Assembler is described in the accompanying Acorn Desktop Development Environment user guide.

## Assembler tools

The assemblers provided include the following features:

- full support of the ARM instruction set

- global and local label capability

- powerful macro processing

- comprehensive expression handling

- conditional assembly

- repetitive assembly

- comprehensive symbol table printouts

- pseudo-opcodes to control printout

### AAsm and Objasm

The Assembler AAsm produces binary image files which can be executed immediately, for example using a \*imagefile command. A variant of AAsm, ObjAsm, creates object files which cannot be executed directly, but must first be linked using the Link tool. It is often most efficient to construct larger programs from several portions, assembling each portion with ObjAsm before linking them all together with Link. Object files linked with those produced by ObjAsm may be produced from some programming language other than assembler, for example C.

The Link tool is described in the accompanying Acorn Desktop Development Environment user guide, in the non-interactive tool section.

### This user guide

This document is a reference guide to the Assemblers working as part of the Development Environment of Acorn Desktop Assembler. These assemblers are the only tools in the Acorn Desktop Assembler product which are not used for programming in other languages; the others are described in the accompanying *Acorn Desktop Development Environment* user guide. It is assumed that you are familiar with other relevant Archimedes documentation, such as the:

- Archimedes Welcome guide

- Archimedes User guide

- Programmer's reference manual

A good introduction to writing programs in Assembler on Archimedes is ARM *Assembly Language Programming* by P.J. Cockerell, (Computer Concepts/MTC, 1987).

### Note on program examples

Both general and specific examples of syntax and screen output are given but there are occasions where the full syntax of an instruction and its accompanying screen appearance would obscure the specific points being made. It follows, therefore, that not all the examples given in the text can be used directly since they are incomplete.

# Conventions used in this manual

The Assembler has its own interpretations of the punctuation symbols and special symbols which are available from the keyboard. These are:

| ! | u | # | \$ | % | 3 | ^ | @ | ( | ) |

|---|---|---|----|---|---|---|---|---|---|

| 1 | 1 | { | }  | 1 | : |   | 5 | 1 | + |

|   |   |   |    |   |   |   | - |   |   |

In order to distinguish between characters used in syntax and descriptive or explanatory characters, typewriter style typeface is used to indicate both text which appears on the screen and text which can be typed on the keyboard. This is so that the position of relevant spaces is clearly indicated.

The following typographical conventions are used throughout this manual:

| Convention    | Meaning                                                                                               |

|---------------|-------------------------------------------------------------------------------------------------------|

| filename      | Text that you must replace with the name of a file, register, variable or whatever is indicated.      |

| &1C           | Hexadecimal numbers are preceded with an ampersand.                                                   |

| {instruction} | Curly brackets {} enclose optional items in the syntax.                                               |

|               | For example, the Assembler AAsm accepts a three field source line which may be expressed in the form: |

|               | {instruction} {label} {;comment}                                                                      |

| ALIGN         | Text that you type exactly as it appears in the manual. For example:                                  |

|               | L321 ADD Ra,Ra,Ra,LSL #1 ;multiply by 3                                                               |

|               |                                                                                                       |

The abbreviation 'DDE' is used in later chapters to mean 'Desktop Development Environment'.

# Part 1 - Using the assemblers

# Assemblers and the DDE

The two versions of the ARM macro assembler, AAsm and ObjAsm, are the only tools included in Acorn Desktop Assembler which are specific to programming in assembly language, hence are described in this volume. All other tools, such as the editor and debugger, are described in detail in the accompanying Acorn Desktop Development Environment user guide.

AAsm and ObjAsm both fit into the non-interactive class of DDE tools, which means that, once you have started an assembly process and chosen a set of options, you cannot interact with it to modify its behaviour, except to view output and pause or stop it (interactive DDE tools, such as the DDT debugger, do allow interaction). All non-interactive DDE tools have several features in common. These are described in detail in the chapter entitled *General features* in the accompanying *Acorn Desktop Development Environment* user guide.

To load AAsm or ObjAsm onto the desktop, open a directory display on the DDE directory of your work disk and double click on !AAsm or !ObjAsm. The AAsm or ObjAsm icon then appears on the icon bar. These have the standard screwdriver and spanner appearance of all the non-interactive DDE tools:

From these icons you have access to the interface to set options and start assembly tasks unmanaged by Make. For more details of these interfaces and their use, see the chapters entitled AAsm and Objasm later in this volume.

# Using the assemblers through Make

The DDE Make tool is designed to manage the efficient construction of programs and libraries, usually from several source files. It avoids needless re-processing of unaltered source files and ensures consistent construction by a method specified in a Makefile. For more Make details see the chapter entitled Make in the accompanying Acorn Desktop Development Environment user guide. ObjAsm and AAsm, like the other non-interactive DDE tools, can be used by Make to process files. When managed by Make the assemblers are controlled by command lines issued by Make, and their icons need not be present on the icon bar. You don't need to double click on !ObjAsm or !AAsm before starting a Make job using these tools. The command lines issued by Make to the assemblers are calculated from the contents of the Makefile controlling the job in progress. The command lines understood by ObjAsm and AAsm are described in the chapters entitled *ObjAsm* and *AAsm* later in this volume.

If you have a machine with two megabytes or more you do not need to understand the details of the command lines contained in your Makefiles; you can adjust them using the same desktop interface as that available from each tool's icon. To do this you follow the Make **Tool options** menu item and click on the name of the tool concerned.

### **Editor throwback**

During development of a program you may well find that you spend a high proportion of your time repeatedly editing, assembling, and testing programs. This development cycle can be speeded up by using Throwback to the SrcEdit editor to assist in removing assembly errors from your sources.

If SrcEdit and the DDEUtils module are loaded and you choose the assembler Throwback option, then perform an assembly of a file causing an assembly error, a browser window is presented by the editor. Double clicking Select on an error line in this browser window makes the editor open an edit window displaying the source file causing the error, with the offending line in view and highlighted, ready for correction. This facility can be used whether assembly is being performed managed by Make or by using the assembler icon bar interfaces.

#### Example throwback session

First double click on !SrcEdit, !ObjAsm and !Link in a directory display to load them as applications with icons on the icon bar. Next open a directory display on the subdirectory User.AssemErr.s to show the text file AssemErr containing the source of the program example of that name.

AssemErr is a simple assembly language program which when run prints Hello World on the screen. It is written to be assembled to an object file by ObjAsm then linked to form an executable image file with Link. Its source contains a simple error which will be detected by ObjAsm when you try to assemble it. Drag the source file AssemErr to the ObjAsm icon. The ObjAsm SetUp dialogue box will appear with the Source filename initialised to the absolute file name. Ensure that the **Throwback** option is enabled: the correct dialogue box appearance is:

| 6 8                  | ObjAsm                       |

|----------------------|------------------------------|

| Source: dDisc4.      | \$.User.AssemErr.s.AssemErr] |

| Options<br>Throwback | Debug                        |

| Run                  | Cancel                       |

Click Menu on the dialogue box and ensure that the **Work directory** item on the menu displayed has the default setting of 'A'. Next click on **Run** on the dialogue box to start assembly. This has the normal effect of removing the dialogue box and putting the ObjAsm output display on the screen, but almost immediately afterwards the assembler will produce an error and request SrcEdit to display a throwback error browser:

| 6 8        |                 |          | Throwback                         | 9 |

|------------|-----------------|----------|-----------------------------------|---|

| Processing | File: add       | s::Har   | d4.\$.UserAsm.AssemErr.s.AssemErr | Û |

| Errors in: | adfs::Ha        | ·d4.\$.U | lserRsm.AssemErr.s.AssemErr       |   |

| Line<br>31 | Type<br>Serious | Error    | Description<br>Unexpected operand | 7 |

| ¢ [        |                 |          | \$                                | Ð |

Double click Select on the assembler error message Unexpected operand in the browser. SrcEdit will display the source file with the line that caused the error clearly highlighted:

| 08    | adf                    | s::HardDisc4.\$.User.Ass      | emErr.s.AssemErr   | ĥ |

|-------|------------------------|-------------------------------|--------------------|---|

| ; Now | for the                | actual program code           |                    | ₽ |

|       | ENTRY                  |                               | ; ObjAsm entry poi |   |

|       | SWI<br>Mov             | OS_GetEnv<br>r13, r1          | ; set up stack poi |   |

|       | SWI<br>= "Hel<br>Align | OS WriteS<br>lo Morld"13,10,0 | ; confirm job done |   |

|       | SWI                    | OS_Exit                       |                    |   |

|       | END                    |                               |                    | п |

| \$    |                        |                               | \$                 | Ð |

Examining this line closely shows that a comma is missing after the close quote. Insert this comma in SrcEdit and save the file. Click Select on the ObjAsm icon and click the **Run** icon to repeat the last assembly. If you have changed the AssemErr source correctly, the assembly should now complete with no errors and without bringing back the SrcEdit browser.

When the ObjAsm save dialogue box appears, click on the **OK** icon to save the object file produced in the o subdirectory next to the s subdirectory containing the source. Drag this object file to the Link icon on the icon bar. The Link SetUp dialogue box appears:

| 6 8                            | Linker                      |                  |

|--------------------------------|-----------------------------|------------------|

| Files: fs::H                   | lardDisc4.\$.User.AssemE    | rr.o.AssemErr]   |

| Options -<br>③ AIF<br>◇ Module | ◇Relocatable AIF<br>◇Binary | Debug<br>Verbose |

| Run                            |                             | Cancel           |

On this dialogue box and its associated menu ensure that the default output type of AIF is chosen, then click on the **Run** action icon. Save the resultant output file in a suitable directory such as the AssemErr subdirectory, then double click Select on its name. The image file should now run, printing the Hello World message in a RISC OS run window:

| Hello | Run<br>World | adf | s::Har | dDisc4 | ,\$, | Jser.As | semErr | , !Run | Image |    |

|-------|--------------|-----|--------|--------|------|---------|--------|--------|-------|----|

| Press | SPACE        | or  | click  | mouse  | to   | contin  | ue     |        |       |    |

|       |              |     |        |        |      |         |        |        |       |    |

|       |              |     |        |        |      |         |        |        |       | 13 |

|       |              |     |        |        |      |         |        |        |       |    |

## **DDT** debugging

If you wish to debug your constructed program with the DDT debugger, you should use only the ObjAsm assembler, as AAsm does not provide sufficient symbol information in its output files to allow more than a few DDT features to work.

DDT can debug assembly language programs at machine level (ie displaying the current execution position on a disassembly of memory) or at source level (ie displaying the current execution position as a source file line). If you wish to debug at source level, the Debug option of ObjAsm must be enabled during assembly.

Insert the ObjAsm KEEP directive (without a following symbol name) in each source file to make this assembler output all symbol information. Your link operation to produce the executable image file to debug with DDT must have the Debug option selected. See the chapter entitled Directives for more details of KEEP.

Executing a binary produced in the above way, or dragging it from a directory display to the DDT icon, starts a DDT debugging session on it. See the chapter entitled *Desktop debugging tool* in the accompanying *Acorn Desktop Development Environment* user guide for more details of DDT.

### Example DDT session

This session demonstrates machine level debugging of assembly language with DDT (see above for the meaning of machine level).

First double click on !DDT, !ObjAsm and !Link in a directory display to load them as applications with icons on the icon bar. Next open a directory display on the subdirectory User.Buggy.s to show the text file Buggy (containing the source of the program example of that name).

Buggy is a small assembly language program which when run is designed to print a list of four hexadecimal random numbers on the screen. It is first assembled with ObjAsm to an object file, then this object is linked with the PrintLib library in User.PrintLib.o to form an executable image file. A fault has been deliberately put in Buggy to illustrate the use of the DDT debugger. The directive KEEP is in the Buggy source file to retain symbol names so that they appear in DDT displays.

Drag the text source file of Buggy to the ObjAsm icon on the icon bar to bring up the ObjAsm SetUp dialogue box, then click **Run** to start assembly. Save the object file produced, then drag it to the Link icon. The Link SetUp box will appear. To link with the PrintLib library, drag this file from User.PrintLib.o to **Input files**. Ensure that the output format is AIF on the SetUp box, and click **Run**. Save the executable image file in a suitable place, then double click Select on it. The program should run, but incorrectly display only one random number:

> Run adfs::HardDisc4.\$.User.Buggy.!RunImage Four hexadecimal random numbers follow: 6F62R954

Press SPACE or click mouse to continue

Now we can determine what the problem is using DDT. A quick inspection of the source code in a SrcEdit window shows that the program is clearly intended to display four random numbers. You may be able to spot the fault in the program text, but here's a way of doing it with DDT.

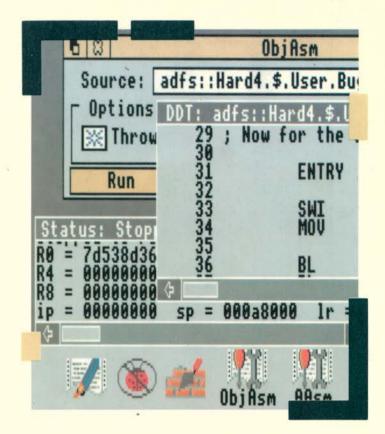

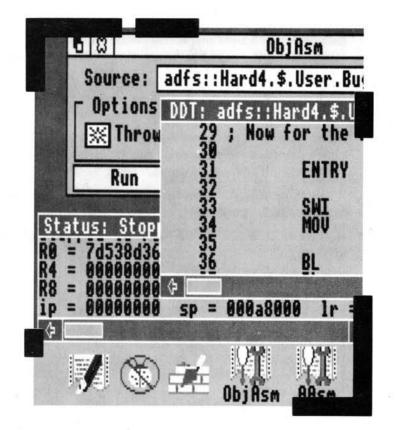

Repeat the link step by clicking Select on the Link icon bar icon, this time selecting the Debug option on the SetUp box before clicking on **Run**. This produces a file with an associated icon which has a black bug displayed on it. Double clicking on this (or dragging it to the DDT icon) loads it into DDT. The two main DDT windows appear:

| 00007ff8:<br>00007ffc:<br>00008008:<br>0008008:<br>0008008:<br>0008008:<br>00088010:<br>00088014: | eb00001b<br>ef000011                   | andeq<br>dcb<br>blnv<br>blnv<br>bl<br>bl<br>swi<br>andeq | r0,r0,r2<br>",",0,0,0<br>&00008000<br>&0000800c<br>&00008040<br>C\$\$code<br>OS_Exit<br>r0.r0.r8.asr | ; &00008080<br>#&02 |     |

|---------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------|-----|

|                                                                                                   |                                        |                                                          | Status: Initia                                                                                       | alisation           | 0   |

| No source<br>Can't set I<br>RO area lin                                                           | level debu<br>breakpoint<br>mit not on | igging<br>on pro<br>page                                 | information<br>ocedure main<br>boundary, last                                                        | page not protected  | ¢ 2 |

Clicking Menu on either DDT window displays the DDT menu, from which you gain access to its many features. For a detailed description of these see the chapter entitled *Desktop debugging tool* in the accompanying *Acorn Desktop Development Environment* user guide. Click Select on the **Single step** item to bring up the single step dialogue box:

| 8            | Single step           |

|--------------|-----------------------|

| 🐹 Ster       | o into procedures     |

| <b>⊘</b> Ste | p by source statement |

| <b>⊘</b> Ste | p by ARM instruction  |

| No. of       | steps: 1 OK           |

Set this as above to step into procedures by ARM instruction. Click once or twice on the **OK** icon and watch the program execution step forward. For the first few instructions you will not recognise the code executed, it is initialisation code added by Link. Carry on until you reach |C\$\$code| – the Buggy code you assembled. Now return to the DDT menu, Select **Display**, and start an updated display of the ARM registers:

| S Update    |              | Base:   |

|-------------|--------------|---------|

| Source      | Expression   | Symbols |

| Disassembly | Memory       |         |

| Arguments   | Registers    | Locals  |

| Backtrace   | FP Registers |         |

Continue single stepping, watching the registers change in the display window. An example pair of main windows is:

| .Buggy.Buggy                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>€</b>                                                                                                                                                            |

| ; &000080f0<br>; &0000811c                                                                                                                                          |

| le Stepping   €   Ø                                                                                                                                                 |

| 11 - Stepping         \$           R3 = 00008148         \$           R7 = 0000000         \$           Fp = 00008014         \$           pc = 000080c4         \$ |

|                                                                                                                                                                     |

When you reach the main top level printing loop, you should see what the problem is.

The procedures rand\_word and print\_hex obey the ARM Procedure Call Standard as applied to leaf procedures (those that call no others). This standard permits called procedures to alter r0 to r3 (any return integer being in r0). The main top level printing loop incorrectly uses r1 as an index, which is then altered by print\_hex to a negative number, terminating the loop. Change the register used for this index to r4, and all will be well:

| Run adfs::HardDisc4.\$.User.Buggy.!RunImage                                             |  |

|-----------------------------------------------------------------------------------------|--|

| Four hexadecimal random numbers follow:<br>51611466<br>B9F6E1AC<br>32E1B3F8<br>024F59D8 |  |

| Press SPACE or click mouse to continue                                                  |  |

|                                                                                         |  |

### Using FrontEnd on your programs

FrontEnd is a relocatable module supplied as part of the Acorn Desktop Assembler product which provides RISC OS desktop interfaces for non-interactive command line programs. The DDE non-interactive tools (such as AAsm and ObjAsm) are each command line programs supported in RISC OS by FrontEnd. This converts each tool into a fully multitasking windowed RISC OS application. For more details of non-interactive DDE tools see the chapters entitled *Working in the* DDE and *General features* in the accompanying *Acorn Desktop Development Environment* user guide.

You can use the power of FrontEnd to produce your own RISC OS applications. To do this you need to construct

- a suitable command line program;

- a Templates file (constructed with FormEd);

- a Sprites file (constructed with Paint);

- a !Run file;

- a !Help text file containing a short description of your program;

- a Messages text file;

- a Desc front end description file.

To be suitable, your command line program has to be non-interactive; ie started with a command line, then running to error or completion without any further user interaction, and outputting reports as screen text. An assembler such as ObjAsm fits this description, and an editor such as SrcEdit does not.

The Desc front end description file contains a specification of the appearance and function of the desktop interface to be provided for your program by FrontEnd. It is written in a special description language understood by FrontEnd. For more details of how to produce this file see the chapter entitled *Extending the* DDE in the accompanying *Acorn Desktop Development Environment* user guide. You may find it easier to make this file by altering a description belonging to one of the non-interactive tools rather than writing your own from scratch.

The Scramble example in your User directory is an example of a simple command line program written in assembler and provided with a desktop interface by FrontEnd.

User.!Scramble.scramble is the command line tool, with the corresponding assembly language source in User.!Scramble.s. It is a very basic command line program, knowing nothing of RISC OS windows or multitasking. It scrambles the contents of a text file to an unreadable jumble for security purposes. Repeating a scramble of a file with an identical code string unscrambles the file. The command line syntax of scramble is:

\*scramble filename -code code\_text

The Sprites file of Scramble has been adapted (by simply renaming the appropriate sprite to !Scramble) from that of one of the non-interactive DDE tools, so the Scramble icon bar icon has the familiar spanner and screwdriver appearance, but there is no need for your programs to have icons like this; just produce your own Sprites file with Paint.

After assembling s.scramble, double click on !Scramble in the User directory display to run it. Double click on !Scramble with the Shift key down to inspect the files which produce this effect. The Scramble SetUp dialogue box appears as:

| ងន    | Scramble |        |

|-------|----------|--------|

| File: | 1        |        |

| Code: | text     |        |

| Run   |          | Cancel |

### Making your own linkable libraries

Linkable libraries, which are usually filed in o subdirectories like object files, are collections of many object files stored in one file. When presented to Link as an input file, the referenced object files within a library are linked into the output file, but those not needed are left out. A linkable library is therefore a recommended

way of storing a selection of useful procedures for re-use in a number of programs. You may find that this facility can save you a lot of time by avoiding continually 'reinventing the wheel'.

The tool used to construct and modify linkable libraries is LibFile. The tool DecCF can also be used to decode some information about an existing library.

The programming example PrintLib, which you can find in User.PrintLib, consists of three potentially useful procedures written in assembler which are intended to be assembled to object files using ObjAsm and then formed into a library with LibFile. They illustrate various programming points as well as how to construct a library.

If you examine the assembler source files in User.PrintLib.s you will see that the procedure exported by each file obeys the ARM Procedure Call Standard. This ensures that they, and hence the PrintLib library, can be linked with other languages such as C. It is essential that procedures placed in a library have consistent register conventions, so that they can be re-used later without consulting their source text.

The PrintLib example is provided with both its assembly language source and the finished library. The facilities provided by this library are used in other programming examples. The procedures it exports are:

| print_string | Print a null terminated string pointed to by r0.                                        |

|--------------|-----------------------------------------------------------------------------------------|

| print_hex    | Print in hexadecimal an integer contained in r0.                                        |

| print_double | Print in scientific format a double precision floating point number contained in r0,r1. |

To reconstruct PrintLib from its sources, first double click on !ObjAsm and !LibFile in a directory display to load them as applications with icons on the icon bar. Then assemble s.PrintStr, s.PrintHex and s.PrintDble to corresponding object files by dragging each source file to the ObjAsm icon and saving the output object files in the default places, ie o.PrintStr.o.PrintHex and o.PrintDble. Next drag o.PrintStr to the Libfile icon to make the LibFile SetUp dialogue box appear:

| 6 🛙                   | Li               | bFile     |            |

|-----------------------|------------------|-----------|------------|

| Libr                  | ary:             |           |            |

| File L                | ist: c4.\$.User. | PrintLib. | o.PrintStr |

| Optio<br>∲Cre<br>♦Ins |                  | List      | library    |

| Run                   |                  |           | Cancel     |

Ensure that the **Create** option is chosen as above. Drag the other two object files to **File List**, then click on **Run**. Finally save the library file produced: it is now ready to use.

The assembly language source file User.PrintLib.s.Test is an example program making use of the procedures exported by PrintLib. To use it:

- 1 Double click on the !Link application to load it.

- 2 Assemble s. Test to o. Test with ObjAsm.

- 3 Link o.Test with the finished PrintLib library to produce an executable AIF image file.

Running the test program by double clicking on it should result in text output into a RISC OS output window:

|                               | Run   | adfs::Har | dDisc4. | \$.User. | PrintLib | .!RunImag | e |

|-------------------------------|-------|-----------|---------|----------|----------|-----------|---|

| Hello  <br>09ABCDE<br>-1.2346 | EF    |           |         |          |          |           |   |

| Press S                       | SPACE | or click  | mouse   | to conti | nue      |           |   |

|                               |       |           |         |          |          |           |   |

|                               |       |           |         |          |          |           |   |

# AAsm

Assm is one of the two ARM assemblers forming part of the Acorn Desktop Assembler product. It processes a text file containing program source written in ARM assembly language into an executable image file or relocatable module. AAsm multitasks under the RISC OS desktop, allowing other tasks to proceed while it operates.

An example use of AAsm is to construct a binary image file !RunImage in a RISC OS desktop application from a source file s.myprog. AAsm processes the source file directly to form !RunImage without the use of Link.

AAsm should not be used to assemble programs to be debugged using the DDT debugger - use ObjAsm instead. AAsm provides the most direct way of processing assembly language source into a runnable image file, and can be convenient for assembling small programs working unmanaged by the Make tool. The other assembler, ObjAsm, is more suitable for processing complex programs, as AAsm forces you to assemble a program in one chunk, using directives GET and LNK to join source files together at assembly time. This means that everything has to be reassembled if you make a change to one source file. ObjAsm has to be used if you wish to construct a program from a mixture of assembly language and a high level language such as C.

The controls of AAsm are similar to those of other non-interactive DDE tools (for a description of the common features of these tools see the chapter entitled *General features* in the accompanying *Acorn Desktop Development Environment* user guide). You adjust options for the next assembly operation on a setup dialogue box and menu which by default appear when you click Select on the main tool icon or drag a source file to it. Once you have set the required options you click on **Run** and the assembly starts. Output and text messages from the assembler can be displayed in one of two windows and menu options allow you to pause or stop the job at any time.

There is no file type to double click on to start AAsm - AAsm owns no filetype unlike, for example, Draw.

# **Starting AAsm**

Like other non-interactive DDE tools, AAsm can be used under the management of Make, with its assembly options specified by the makefile passed to Make. For such managed use, AAsm is started automatically by Make, you don't have to load AAsm onto the icon bar.

To use AAsm directly, unmanaged by Make, first open a directory display on the DDE directory, then double click Select on !AAsm. The AAsm main icon appears on the icon bar.

Clicking Select on this icon or dragging an assembly language source file from a directory display to this icon brings up the AAsm SetUp dialogue box:

| 6 8     | AAsm   |

|---------|--------|

| Source: | 1      |

| Options |        |

| Run     | Cancel |

**Source** will appear containing the name of the last filename entered there, or empty if there isn't one.

Dragging a file on to the icon will bring up the dialogue box and automatically insert the dragged filename as the **Source** file.

Clicking Menu on the SetUp dialogue box brings up the AAsm SetUp menu:

| AAsm            |    |

|-----------------|----|

| Command line    | ¢  |

| √ Stamp         |    |

| Cross reference | ce |

| Print           |    |

| NoTerse         |    |

| Width           | ¢  |

| Length          | ¢  |

| Module          |    |

| √ NoCache       |    |

| √Work directory | 4  |

| MaxCache        | ♦  |

| C strings       |    |

The SetUp dialogue box and menu specify the next assembly job to be done. You start the next job by clicking **Run** on the dialogue box (or Command line menu dialogue box). Clicking **Cancel** removes the SetUp dialogue box and clears any changes you have just made to the options settings back to the state before you brought up the SetUp box. The options last until you adjust them again or !AAsm is reloaded. You can also save them for future use with an option from the main icon menu.

# AAsm SetUp options

When the SetUp dialogue box is displayed the **Source** writable icon contains the name of the sourcefile to be assembled. The sourcefile can be specified in two ways:

- If the SetUp box is obtained by clicking on the main AAsm icon, it comes up with the sourcefile from the previous setting. This helps you repeat a previous assembly, as clicking on the **Run** action button repeats the last job if there was one.

- If the SetUp box appears as a result of dragging a source file containing assembly language text to the main icon, the source file will be the same as the dragged source file.

When the SetUp box appears the Source icon has input focus, and can be edited in the normal RISC.OS fashion. If a further source file is selected in a directory display and dragged to **Source**, its name replaces the one already there.

### Setup dialogue box options

The **Throwback** option switches editor throwback on or off. When enabled, if the DDEUtils module and SrcEdit are loaded, any assembly errors cause the editor to display an error browser. Double clicking Select on an error line in this browser makes the editor display the source file containing the error, with the offending line highlighted. See the chapter entitled *SrcEdit* in the accompanying *Acorn Desktop Development Environment* user guide for more details.

Throwback is on by default.

### Setup menu options

The AAsm RISC OS desktop interface works by driving an AAsm tool underneath with a command line constructed from your SetUp options. The **Command line** item at the top of the SetUp menu leads to a small dialogue box in which the command line equivalent of the current SetUp options is displayed:

| AAsm                                | Command Line:                              |

|-------------------------------------|--------------------------------------------|

| Command line ♥<br>√Stamp            | ModeEx.s.ModeEx -ThrowBack -Stamp -NoCache |

| Cross reference<br>Print<br>NoTerse |                                            |

| Width \$                            |                                            |

| Length ¢<br>Module<br>√NoCache      |                                            |

| √Work directory ♦                   |                                            |

| MaxCache ¢<br>C strings             |                                            |

Clicking on **Run** in this dialogue box starts assembly in the same way as clicking on **Run** in the main SetUp box. Pressing Return in the writable icon in this box has the same effect. Before starting assembly from the command line box, you can edit the command line textually, although this is not normally useful.

Stamp causes any output image files to have up to date timestamps.

Stamp is on by default.

When **Cross reference** is enabled (with a tick next to it) an alphabetically sorted cross reference of all symbols encountered is output after assembly. Note that the text output may be very large for a big program and so this option may not function on a machine with restricted memory.

Cross reference is off by default.

The **Print** option enables assembler source code to be viewed directly from the SrcEdit editor or from within the Assembler. This option turns on the Assembler screen listing, and during assembly the source code, object code, memory addresses and reference line numbers will be printed on the screen.

Print is off by default.

**NoTerse** modifies the effect of the **Print** option. If **NoTerse** is not enabled, **Print** only outputs the conditionally assembled parts of your program, but with **NoTerse** enabled (accompanied by a tick), conditionally non-assembled parts are listed as well.

NoTerse is off by default.

Width allows you to specify assembler output width:

| AAsm                            |        |

|---------------------------------|--------|

| Command line ⊀                  | 2      |

| √ Stamp                         |        |

| <b>Cross reference</b>          |        |

| Print                           |        |

| NoTerse                         | Width: |

| Width 🕏                         | 132    |

| Length 🕏                        |        |

| Module                          |        |

| √ NoCache                       |        |

| √Work directory &<br>MaxCache s | >      |

| MaxCache 4                      | >      |

| C strings                       |        |

This should be specified as an integer between 1 and 254. A width of 76 is suitable for a Mode 12 RISC OS window.

The default width is 131.

**Length** allows you to specify the number of lines per page for printer output. At the end of each page the assembler inserts a form feed character.

The default length is 60.

Enabling the **Module** option is the way to produce a relocatable module as an AAsm output file rather than an executable imagefile. This option is present with AAsm but not ObjAsm, since ObjAsm always produces linkable object files as its output, and producing a relocatable module from object files is enabled with the options of the Link tool.

Module is off by default.

When **NoCache** is switched off cacheing is enabled. AAsm is a two pass assembler - it examines each source file twice. To avoid reading each source file twice from disk the assembler can cache the source in memory, reading it from disk for the first pass, then storing it in RAM for the second.

Cacheing is a very heavy user of memory, making it unsuitable for smaller machines.

NoCache is by default on - cacheing off.

| AAsm            |    |            |

|-----------------|----|------------|

| Command line    | €  |            |

| √ Stamp         |    |            |

| Cross reference |    |            |

| Print           |    |            |

| NoTerse         |    |            |

| Width           | ⇔  |            |

| Length          | \$ |            |

| Module          |    |            |

| √ NoCache       |    | Directory: |

| √Work directory | €  | 1          |

| MaxCache        | \$ |            |

| C strings       |    |            |

Work directory allows you to specify the work directory:

The GET and LNK directives both result in the assembler loading source files specified with the directive. The work directory is the place where these source files are to be found. An example is a source file adfs::4.\$.user.s.foo containing the line:

GET s.macros

If the work directory is ^ then the file loaded is:

adfs::4.\$.user.s.^.s.macros

(ie adfs::4.\$.user.s.macros)

The work directory must be given relative to the position of the source file containing the GET or LNK, without a trailing dot.

The default work directory is ^.

**MaxCache** allows you to specify the maximum amount of RAM to be used for cacheing source files (when **NoCache** is off). The maximum cache is specified in megabytes.

The default MaxCache is 8Mb - effectively unlimited.

**C strings**, when enabled, allows the assembler to accept C style string escapes such as '\n'. **C strings** is not enabled by default, as it results in '\' characters in string constants being interpreted in a different way compared to previous Acorn assemblers.

# AAsm output

AAsm outputs text messages as it proceeds. These include source listings and symbol cross references (described in the previous section). By default any such text is directed into a scrollable output window:

This window is read-only: you can scroll up and down to view progress, but you cannot edit the text without first saving it. To indicate this, clicking Select on the scrollable part of this window has no effect.

The contents of the window illustrated above are typical of those you see from a successful assembly; the title line of the assembler with version number, followed by no error messages.

Clicking Adjust on the close icon of the output window switches to the output summary dialogue box. This presents a reminder of the tool running (AAsm), the status of the task (Running, Paused, Completed or Aborted), the time when the task was started and the number of lines of output that have been generated (ie those that are displayed by the output window).

| 0 3   | AAsm (Completed)  |

|-------|-------------------|

| 11    | Run at: 17:43:01  |

| AAsm  | 1 Lines of output |

| Abort | Continue          |

Clicking Adjust on the close icon of the summary box returns to the output window.

Both the above AAsm output displays follow the standard pattern of those of all the non-interactive DDE tools. The common features of the non-interactive DDE tools are covered in more detail in the chapter entitled *General features* in the accompanying *Acorn Desktop Development Environment* user guide. Both AAsm output

displays and the menus brought up by clicking Menu on them offer the standard features allowing you to abort, pause or continue execution (if the execution hasn't completed), and to save output text to a file or repeat execution.

AAsm error messages appear in the output viewer, with copies in the editor error browser when throwback is working. *Appendix* A - Error messages at the end of this manual contains a list of all the AAsm error messages together with brief explanations.

Assembly listings and cross references appearing in the output window are often very large for assemblies of complex source files. The scrolling of the output window is useful to view them, and to investigate them with the full facilities of the source editor. You can save the output text straight into the editor by dragging the output file icon to the SrcEdit main icon on the icon bar.

### AAsm icon bar menu

The AAsm main icon bar menu follows the standard pattern for non-interactive DDE tools:

| AAsm      |     |

|-----------|-----|

| Info      | \$  |

| Save opti | ons |

| Options   | 4   |

| Help      |     |

| Quit      |     |

**Save options** saves all the current AAsm options, including both those set from the SetUp dialogue box and from the Options item on this menu. When AAsm is restarted it is initialised with these options rather than the defaults.

The **Options** submenu allows you to set the following options:

**Display** specifies the output display as either a text window (default) or as a summary box.

If **Auto run** is enabled, dragging a source file to the AAsm main icon immediately starts an assembly with the current options rather than displaying the SetUp box first.

If **Auto save** is enabled output image files are saved to suitable places automatically without producing a save dialogue box for you to drag the file from.

Both Auto run and Auto save are off by default.

| 8                    | AAsm help                                                                                                |           |

|----------------------|----------------------------------------------------------------------------------------------------------|-----------|

| Rasm                 |                                                                                                          |           |

| Purpose: Absolute as | sembler                                                                                                  |           |

| Setup:<br>Icon       | Action/Meaning                                                                                           | Default   |

| Source<br>Throwback  | Name of file to be assembled<br>(either typed or dragged)<br>Report errors and warnings to the<br>editor | nil<br>on |

| Menu:<br>Entry       | Action/Meaning                                                                                           | Default   |

| Stamp                | Timestamp the object produced                                                                            | on        |

Clicking on **Help** on the main AAsm menu displays a short text summary of the various SetUp options, in a scrollable read-only window:

### Example AAsm session

The programming example ModeEx is a relocatable module written in assembly language processed from text source to usable module with AAsm. The ModeEx relocatable module, when rmloaded, provides an extra screen mode, mode 29. Unless you alter the parameters in the source file, mode 29 is similar to mode 12 in having 16 colours, but has no borders, allowing 96 by 36 characters on the screen instead of 80 by 32. You may well find this mode a useful one in which to work with the DDE, as it offers a useful compromise between character size and information visible.

To construct this module, first double click on !AAsm to load it as an application with an icon on the icon bar. The source of ModeEx is in the subdirectory User.ModeEx.s. Drag the text source file to the AAsm icon to make the AAsm SetUp box appear:

| b | 8   | AAsm                                    |   |

|---|-----|-----------------------------------------|---|

|   | Sou | rce: [:HardDisc4.\$.User.ModeEx.s.ModeE | X |

|   |     | tions —<br>Throwback                    |   |

| Ē |     | Run Cancel                              |   |

Set the Module option on the SetUp menu to on, then click on **Run**. The module will then assemble, so you can save it and use it.

#### AAsm managed by Make

When Acorn Desktop Assembler is installed on your system, Make understands ObjAsm, not AAsm, as the tool to process assembly language source from s subdirectories.

To use AAsm managed by Make, ie driven by a recipe stored in a Makefile created by Make, store your source in a directory not having the recognised name s. When first creating your project in the New project dialogue box, specify AAsm as the tool creating the final target. Drag your top level source file to the **Insert** field of your Project dialogue box and set AAsm **tool options** in the normal way.

For general details of the operation of Make, see the chapter entitled Make in the accompanying Acorn Desktop Development Environment user guide.

#### AAsm command lines

AAsm, in common with the other non-interactive DDE tools, can be driven with a text command line without its RISC OS desktop interface appearing. This enables AAsm to be driven by Make as specified in textual makefiles.

You can use AAsm outside the RISC OS desktop from its command line, in the same way that it could be used in the previous Acornsoft Archimedes Assembler product. However, as all the useful AAsm features can now be more conveniently used from the RISC OS desktop there is little reason for you to do this. The desktop removes the need for you to understand the command line syntax.

The AAsm RISC OS desktop interface drives the AAsm tool underneath by issuing a command line constructed from your SetUp options. The **Command line** SetUp menu option allows you to view the command line constructed in this way.

If you have a machine with more than 1Mb of RAM, the Make tool allows you to construct makefiles with assembly operations specified using the AAsm desktop interface (by following the **Tool options** item of Make). You can therefore construct makefiles without understanding the command line syntax of AAsm.

The command line syntax of AAsm is documented here as a reference.

A command line just consisting of the tool name AAsm causes the assembler to drop into an obsolescent interactive mode, within which you issue commands with the assembler resident in memory. It is not recommended to use this mode, but its syntax is revealed by typing help once it is entered. Interactive mode is left by entering Quit (or Q for short). This mode of use is not covered further here.

The AAsm command line consists of the AAsm tool name followed by a series of keywords, some of which are followed by associated arguments. Each keyword starts with a minus sign (-) and is case independent, but is listed below with its minimum abbreviation in capital letters:

| -FRom filename   | Specifies the source file (the <b>Source</b> item of the SetUp box).                                          |

|------------------|---------------------------------------------------------------------------------------------------------------|

| -TO filename     | Specifies the output image or module file name.                                                               |

| -Stamp           | Time stamps the output image or module file (the SetUp box <b>Stamp Output</b> option).                       |

| -THrowback       | Enables source editor throwback when available (the SetUp box <b>Throwback</b> option).                       |

| -Xref            | When combined with -Quit outputs a sorted cross reference (the SetUp menu <b>Cross reference</b> option).     |

| -Print           | Enables source file listing (the SetUp menu <b>Print</b> option).                                             |

| -NOTerse         | Enlarges source listing (the SetUp menu <b>NoTerse</b> option).                                               |

| -Width number    | Sets output width to an integer number of characters.                                                         |

| -Length number   | Sets output page length to an integer number of lines.                                                        |

| -Module          | Sets output file type to relocatable module (the SetUp menu <b>Module</b> option).                            |

| -NoCache         | Do not cache source files (the SetUp menu <b>NoCache</b> option).                                             |

| -Desktop dirname | Specifies the work directory in which to find GET or LNK files (the SetUp menu <b>Work directory</b> option). |

| -Maxcache number | Specifies the maximum cache size as an integer number of megabytes.                                           |

| -Quit            | Avoids entering interactive mode after assembly - recommended.                                                |

| -Closeexec       | Closes any open exec files if assembly fails.                                                                 |

| -Esc             | Enable C style string escapes (the SetUp menu <b>C strings</b> option).                                       |

-FRom and -TO have no effect unless both are specified. If both are specified, an assembly is performed immediately using the specified files. The parameters belonging to -FRom and -TO may be specified in this order without using the keywords.

# ObjAsm

ObjAsm is one of the two ARM assemblers forming part of the Acorn Desktop Assembler product. It processes text files containing program source written in ARM assembly language into linkable object files. Object files can be linked by the Link tool with each other or with libraries of object files to form executable image files or relocatable modules. ObjAsm multitasks under the RISC OS desktop, allowing other tasks to proceed while it operates.

ObjAsm must be used to assemble programs to be debugged using the DDT debugger. It is more suitable than AAsm for the construction of large programs, as for ObjAsm the sources can be split into several files and only re-assembled to object files when you have altered them.

An example use of ObjAsm is to construct a binary image file !RunImage in a RISC OS desktop application from the two source files s.interface and s.portable. ObjAsm processes the source files to form o.interface and o.portable, which the Link tool processes to form !RunImage.

The controls of ObjAsm are similar to those of other non-interactive DDE tools, with the common features described in the chapter entitled *General features* in the accompanying *Acorn Desktop Development Environment* user guide. You adjust options for the next assembly operation on a setup dialogue box and menu which by default appear when you click Select on the main icon or drag a source file to it. Once you have set options you click on a Run action icon and the assembly starts. While the assembly is running output windows display any text messages from the assembler and allow you to stop the job if you wish.

There is no file type to double click on to start ObjAsm - ObjAsm owns no file type unlike, for example, Draw.

# Starting ObjAsm

Like other non-interactive DDE tools, ObjAsm can be used under the management of Make, with its assembly options specified by the makefile passed to Make. For such managed use, ObjAsm is started automatically by Make, you don't have to load ObjAsm onto the icon bar.

To use ObjAsm directly, unmanaged by Make, first open a directory display on the DDE directory, then double click Select on !ObjAsm. The ObjAsm main icon appears on the icon bar.

Clicking Select on this icon or dragging an assembly language source file from a directory display to this icon brings up the ObjAsm SetUp dialogue box:

| 68      | ObjAsm |

|---------|--------|

| Source: | I I    |

| Options | Debug  |

| Run     | Cancel |

**Source** will appear containing the name of the last filename entered there, or empty if there isn't one.

Dragging a file on to the icon will bring up the dialogue box and automatically insert the dragged filename as the **Source** file.

Clicking Menu on the SetUp dialogue box brings up the ObjAsm SetUp menu:

| ObjAsm           |   |

|------------------|---|

| Command line     | ♦ |

| √ Stamp          |   |

| Cross reference  |   |

| Print            |   |

| NoTerse          |   |

| Width            | ♦ |

| Length           | ♦ |

| √ NoCache        |   |

| √ Work directory | ♦ |

| MaxCache         | ¢ |

| C strings        |   |

The SetUp dialogue box and menu specify the next assembly job to be done. You start the next job by clicking **Run** on the dialogue box (or Command line menu dialogue box). Clicking **Cancel** removes the SetUp dialogue box and clears any changes you have just made to the options settings back to the state before you brought up the SetUp box. The options last until you adjust them again or !ObjAsm is reloaded. You can also save them for future use with an option from the main icon menu.

# **ObjAsm SetUp options**

When the SetUp dialogue box is displayed the **Source** writable icon contains the name of the source file to be assembled. The sourcefile can be specified in two ways:

- If the SetUp box is obtained by clicking on the main ObjAsm icon, it comes up with the sourcefile from the previous setting. This helps you repeat a previous assembly, as clicking on the **Run** action icon repeats the last job if there was one.

- If the SetUp box appears as a result of dragging a source file containing assembly language text to the main icon, the source file will be the same as the dragged source file.

When the SetUp box appears the Source icon has input focus, and can be edited in the normal RISC OS fashion. If a further source file is selected in a directory display and dragged to **Source**, its name replaces the one already there.

#### Setup dialogue box options

The **Throwback** option switches editor throwback on or off. When enabled, if the DDEUtils module and SrcEdit are loaded, any assembly errors cause the editor to display an error browser. Double clicking Select on an error line in this browser makes the editor display the source file containing the error, with the offending line highlighted. See the chapter entitled *SrcEdit* in the accompanying *Acorn Desktop Development Environment* user guide for more details.

#### Throwback is on by default.

The **Debug** option switches on or off the production of debugging tables. When enabled, extra information is included in the output object file which enables source level debugging of the linked image (as long as the Link Debug option is also enabled) by the DDT debugger. If this option is disabled, any image file finally produced can only be debugged at machine level. Source level debugging allows the current execution position to be indicated as a displayed line of your source, whereas machine level debugging only shows the position on a disassembly of memory.

#### Setup menu options

The ObjAsm RISC OS desktop interface works by driving an ObjAsm tool underneath with a command line constructed from your SetUp options. The **Command line** item at the top of the SetUp menu leads to a small dialogue box in which the command line equivalent of the current SetUp options is displayed:

| ObjAsm                 |    |            | Comma  | nd Line: |      |           |

|------------------------|----|------------|--------|----------|------|-----------|

| Command line           | \$ | -Throwback | -Stamp | -NoCache | -des | ktop ^ -T |

| √ Stamp                |    |            |        | *        |      |           |

| <b>Cross</b> reference |    |            |        |          |      | Run       |

| Print                  |    |            |        |          |      |           |

| NoTerse                |    |            |        |          |      |           |

| Width                  | ⇔  |            |        |          |      |           |

| Length                 | ♦  |            |        |          |      |           |

| √ NoCache              |    |            |        |          |      |           |

| √Work directory        | ⇔  |            |        |          |      |           |

| MaxCache               | ♦  |            |        |          |      |           |

| C strings              |    |            |        |          |      |           |

The **Run** action icon in this dialogue box starts assembly in the same way as that in the main SetUp box. Pressing Return in the writable icon in this box has the same effect. Before starting assembly from the command line box, you can edit the command line textually, although this is not normally useful.

Stamp causes any output object files to have up to date timestamps.

Stamp output is on by default.

When **Cross reference** is enabled (with a tick next to it) an alphabetically sorted cross reference of all symbols encountered is output after assembly. Note that the text output may be very large for a big program and so this option may not function on a machine with restricted memory.

Cross reference is off by default.

The **Print option** enables assembler source code to be viewed directly from the SrcEdit editor or from within the Assembler. This option turns on the Assembler screen listing, and during assembly the source code, object code, memory addresses and reference line numbers will be printed on the screen.

Print is off by default.

**NoTerse** modifies the effect of the **Print** option. Without **NoTerse** enabled, **Print** only outputs the conditionally assembled parts of your program, but with **NoTerse** enabled (accompanied by a tick), conditionally non-assembled parts are listed as well.

34

NoTerse is off by default.

Width allows you to specify assembler output width:

| ObjAsm          |    |        |

|-----------------|----|--------|

| Command line    | €  |        |

| √ Stamp         |    |        |

| Cross reference |    |        |

| Print           |    |        |

| NoTerse         |    | Width: |

| Width           | ¢  | 76     |

| Length          | \$ |        |

| √NoCache        |    |        |

| √Work directory | €  |        |

| MaxCache        | ♦  |        |

| C strings       |    |        |

This should be specified as an integer between 1 and 254. A width of 76 is suitable for a Mode 12 RISC OS window.

The default width is 131.

**Length** allows you to specify the number of lines per page for printer output. At the end of each page the assembler inserts a form feed character.

The default length is 60.

When **NoCache** is switched off cacheing is enabled. ObjAsm is a two pass assembler - it examines each source file twice. To avoid reading each source file twice from disk the assembler can cache the source in memory, reading it from disk for the first pass, then storing it in RAM for the second.

Cacheing is a very heavy user of memory, making it unsuitable for smaller machines.

NoCache is by default on - cacheing off.

Work directory allows you to specify the work directory:

| ObjAsm           |    |       |       |

|------------------|----|-------|-------|

| Command line     | \$ |       |       |

| √ Stamp          |    |       |       |

| Cross referenc   | e  |       |       |

| Print            |    |       |       |

| NoTerse          |    |       |       |

| Width            | ⇔  |       |       |

| Length           | ⇔  |       |       |

| √ NoCache        |    | Direc | tory: |

| √ Work directory | €> |       | 1     |

| MaxCache         | \$ |       |       |

| C strings        |    |       |       |

The GET and LNK directives both result in the assembler loading source files specified with the directive. The work directory is the place where these source files are to be found. An example is a source file adfs::4.\$.user.s.foo containing the line:

GET s.macros

If the work directory is ^ then the file loaded is:

adfs::4.\$.user.s.^.s.macros

(ie adfs::4.\$.user.s.macros)

The work directory must be given relative to the position of the source file containing the GET or LNK, without a trailing dot.

The default work directory is ^.

**MaxCache** allows you to specify the maximum amount of RAM to be used for cacheing source files (when **NoCache** is off). The maximum cache is specified in megabytes.

The default maximum cache is 8Mb - effectively unlimited.

**C strings**, when enabled, allows the assembler to accept C style string escapes such as '\n'. **C strings** is not enabled by default, as it results in '\' characters in string constants being interpreted in a different way compared to previous Acorn assemblers.

# **ObjAsm output**

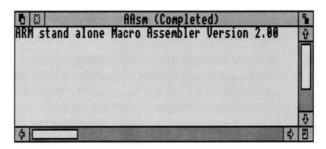

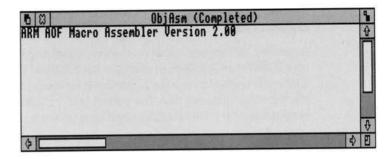

ObjAsm outputs text messages as it proceeds. These include source listings and symbol cross references (as described in the previous sections). By default any such text is directed into a scrollable output window:

This window is read-only: you can scroll up and down to view progress, but you cannot edit the text without first saving it. To indicate this clicking Select on the scrollable part of this window has no effect.

The contents of the window illustrated above are typical of those you see from a successful assembly; the title line of the assembler with version number, followed by no error messages.

Clicking Adjust on the close icon of the output window switches to the output summary dialogue box. This presents a reminder of the tool running (ObjAsm), the status of the task (Running, Paused, Completed or Aborted), the time when the task was started and the number of lines of output that have been generated (ie those that are displayed by the output window).

| 68     | ObjAsm (Completed)                    |

|--------|---------------------------------------|

| 0bjAsm | Run at: 16:51:01<br>1 Lines of output |

| Abort  | Continue                              |

Clicking Adjust on the close icon of the summary box returns to the output window.

Both the above ObjAsm output displays follow the standard pattern of those of all the non-interactive DDE tools. The common features of the non-interactive DDE tools are covered in more detail in the chapter entitled *General features* in the accompanying *Acorn Desktop Development Environment* user guide. Both ObjAsm output displays and the menus brought up by clicking Menu on them offer the standard features allowing you to abort, pause or continue execution (if the execution hasn't completed) and to save output text to a file or repeat execution.

ObjAsm error messages appear in the output viewer, with copies in the editor error browser when throwback is working. Appendix A - Error messages at the end of this manual contains a list of all ObjAsm error messages together with brief explanations.

Assembly listings and cross references appearing in the output window are often very large for assemblies of complex source files. The scrolling of the output window is useful to view them, and to investigate them with the full facilities of the source editor, you can save the output text straight into the editor by dragging the output file icon to the SrcEdit main icon on the icon bar.

#### ObjAsm icon bar menu

The ObjAsm main icon bar menu follows the standard pattern for non-interactive DDE tools:

| ObjAsm       |   |

|--------------|---|

| Info         | ♦ |

| Save options |   |

| Options      | ¢ |

| Help         |   |

| Quit         |   |

**Save options** saves all the current ObjAsm options, including both those set from the SetUp dialogue box and from the **Options** item on this menu. When ObjAsm is restarted it is initialised with these options rather than the defaults.

The **Options** submenu allows you to set the following options:

**Display** specifies the output display as either a text window (default) or as a summary box.

If **Auto run** is enabled, dragging a source file to the ObjAsm main icon immediately starts an assembly with the current options rather than displaying the SetUp box first.

If **Auto save** is enabled output image files are saved to suitable places automatically without producing a save dialogue box for you to drag the file from.

Both Auto run and Auto save are off by default.

Clicking on **Help** on the main ObjAsm menu displays a short text summary of the various SetUp options, in a scrollable read-only window:

| 6 8                       | Objfism help                                                                                             |           | 1 |

|---------------------------|----------------------------------------------------------------------------------------------------------|-----------|---|

| ObjAsm<br>Purpose: ARM as | sembler outputting object files                                                                          |           | Ŷ |

| Setup:<br>Icon            | Action/Meaning                                                                                           | Default   |   |

| Source<br>Throwback       | Name of file to be assembled<br>(either typed or dragged)<br>Report errors and warnings to the<br>editor | nil<br>on |   |

| Menu:<br>Entry            | Action/Meaning                                                                                           | Default   |   |

| Stamp                     | Timestamp the object produced                                                                            | on        | Ą |

| 4                         |                                                                                                          | \$        | 9 |

# Example ObjAsm session

The programming example User.!Scramble is a non-desktop free standing command line program written in assembly language and given a RISC OS desktop interface (ie made into an application) by the FrontEnd module supplied as part of the DDE. Its purpose is to scramble the contents of text files for security. Repeating a scramble of a file with the same code text unscrambles it.

For more details of its support by the FrontEnd module, see the section entitled Using FrontEnd on your programs on page 15.

The assembly language source for scramble is in the subdirectory User.!Scramble.s. The code demonstrates the following points:

- ObjAsm directives needed for a free standing program;

- processing command lines from assembly language;

- random number generation;

- simple file handling;

- register usage by procedures.

To assemble scramble, first double click on !Objasm and !Link in a directory display to load them. Drag the scramble source text file to the ObjAsm icon. The SetUp dialogue box of ObjAsm appears. Check that the default SetUp options are enabled:

| 6 8                 | ObjAsm                      |

|---------------------|-----------------------------|

| Source: Disc4       | .User.!Scramble.s.scramble] |

| Options 📉 Throwback | Debug                       |

| Run                 | Cancel                      |

Click on **Run** to proceed, and save the object file produced in !Scramble.o. Drag the object file to the Link icon, and **Run** Link to produce an AIF executable image file, the link having the scramble object file as its only input file. The command line program is now ready for use.

Try copying the source file for scramble up into the subdirectory User.!Scramble as Test, and move out of the desktop to the command line by

\*scramble filename -code code\_text

pressing F12. The command line syntax of scramble is:

As an experiment, try typing

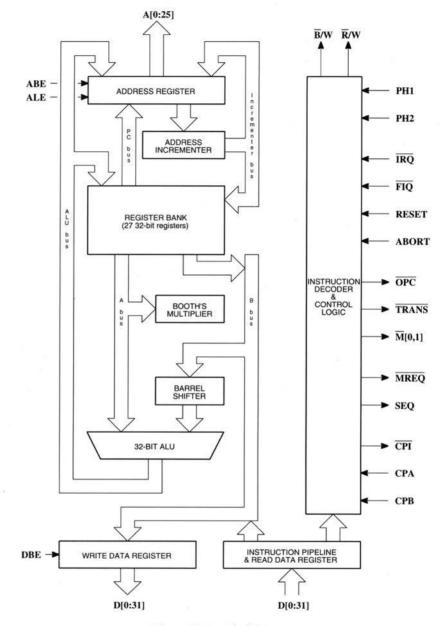

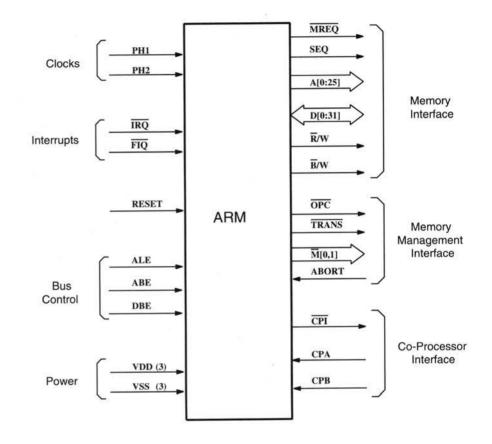

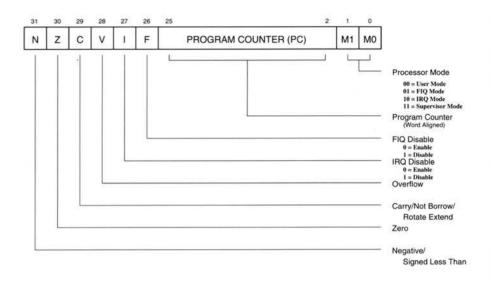

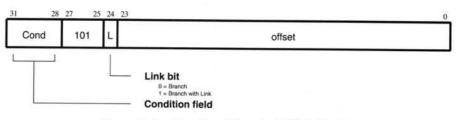

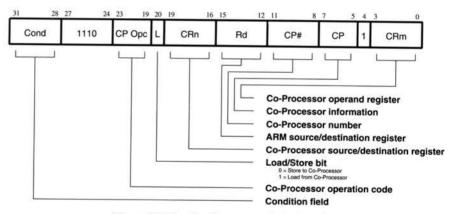

\*dir \$.User.!Scramble \*scramble Test -code DDEIsFriendly